FPGA Reverse Engineering

Anobit PC-00007 Board

FPGA: Virtex 5 XC5VLX110T

Family Overview

Data Sheet: DC ans Switching Characteristics

User Guide

Packaging and Pinout Specification

Configuration User Guide

PCB Designer's Guide

Package Drawing

FF1136 Package Material Declaration

FFG1136 Package Material Declaration

U17

RAM: 5 x Samsung (SEC) K4T1G084QQ (1 GBit DDR2 SDRAM)

Datenblatt

U11, U13, U18, U22, U25

Flash: Micron 25P28V6G (128 MBit Serial Flash)

Datenblatt

U24

Pinout:

CS# - 1 - P31 SO - 2 - P30 (bridge R292) WP - 3 - 3.17V GND - 4 - P35 SI - 5 - P33 SCK - 6 - P32 HOLD- 7 - P43 VCC - 8 - P43

???: Anobit MSP1040-A0 (ASIC?)

U5

RAM: Hynix H27UCG8UDMYR (DDR3 RAM?)

Datenblatt

U7

USB-UART Bridge: FTDI FT2232HQ

Datenblatt

U9

Linear LTC2932 (Supply Monitor)

Datenblatt

U6

Texas Instruments TPS54672 (Schaltregler)

Datenblatt

U27

IDT 844071 (Clock Generator)

Datenblatt

U21

USB UART:

Controller wird korrekt erkannt aber die Verbindung wird kurz danach getrennt.

Getestet mit Board nr: 1

dmesg log:

[15653.129591] usb 4-1.2: Detected FT2232H [15653.129595] usb 4-1.2: Number of endpoints 2 [15653.129599] usb 4-1.2: Endpoint 1 MaxPacketSize 512 [15653.129602] usb 4-1.2: Endpoint 2 MaxPacketSize 512 [15653.129606] usb 4-1.2: Setting MaxPacketSize 512 [15653.132535] usb 4-1.2: FTDI USB Serial Device converter now attached to ttyUSB1 [15654.076033] usb 4-1.2: USB disconnect, device number 4 [15654.076453] ftdi_sio ttyUSB0: FTDI USB Serial Device converter now disconnected from ttyUSB0 [15654.076483] ftdi_sio 4-1.2:1.0: device disconnected [15654.076803] ftdi_sio ttyUSB1: FTDI USB Serial Device converter now disconnected from ttyUSB1 [15654.076825] ftdi_sio 4-1.2:1.1: device disconnected

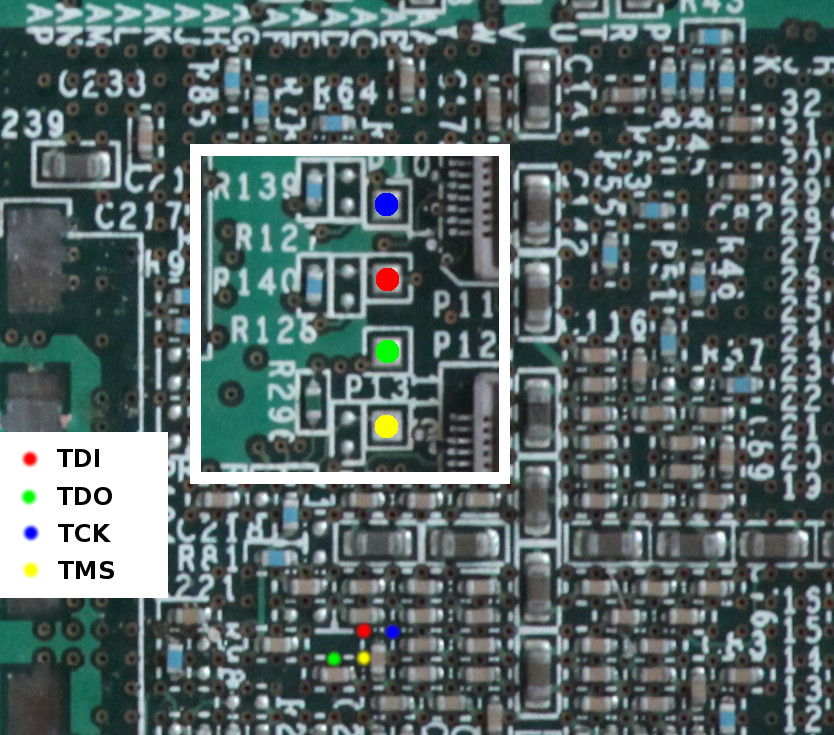

JTAG Pinout:

TDI - AC15 - P11

TDO - AD14 - P12

TCK - AB15 - P10

TMS - AC14 - P13

ISE iMPACT output:

Maximum TCK operating frequency for this device chain: 33000000. Validating chain... Boundary-scan chain validated successfully. 1: Device Temperature: Current Reading: 39.05 C, Min. Reading: 30.20 C, Max. Reading: 39.05 C 1: VCCINT Supply: Current Reading: 1.011 V, Min. Reading: 1.011 V, Max. Reading: 1.017 V 1: VCCAUX Supply: Current Reading: 2.479 V, Min. Reading: 2.476 V, Max. Reading: 2.481 V '1': IDCODE is '01110010101011010110000010010011' '1': IDCODE is '72ad6093' (in hex). '1': : Manufacturer's ID = Xilinx xc5vlx110t, Version : 7 '1': Reading status register contents... CRC error : 0 Decryptor security set : 0 DCM locked : 1 DCI matched : 1 End of startup signal from Startup block : 1 status of GTS_CFG_B : 1 status of GWE : 1 status of GHIGH : 1 value of MODE pin M0 : 1 value of MODE pin M1 : 0 Value of MODE pin M2 : 0 Internal signal indicates when housecleaning is completed : 1 Value driver in from INIT pad : 1 Internal signal indicates that chip is configured : 1 Value of DONE pin : 1 Indicates when ID value written does not match chip ID : 0 Decryptor error Signal : 0 System Monitor Over-Temperature Alarm : 0 startup_state[18] CFG startup state machine : 0 startup_state[19] CFG startup state machine : 0 startup_state[20] CFG startup state machine : 1 E-fuse program voltage available : 0 SPI Flash Type[22] Select : 1 SPI Flash Type[23] Select : 1 SPI Flash Type[24] Select : 1 CFG bus width auto detection result : 1 CFG bus width auto detection result : 1 Reserved : 0 BPI address wrap around error : 0 IPROG pulsed : 1 read back crc error : 0 Indicates that efuse logic is busy : 0